# APPLICATION NOTE

## TDA8766G EVALUATION BOARD DOCUMENTATION

AN96012

Philips Semiconductors

# **APPLICATION NOTE**

## TDA8766G EVALUATION BOARD DOCUMENTATION

## Author : Stéphane DESPROGES

## Application Laboratory - Paris France

## Keywords:

Evaluation board TDA8766G 10 bit ADC Low power ADC high speed ADC

Date : March 15th 1996

## Summary

This note describes a demonstration board which facilitates the evaluation of the TDA8766G 10 bit analog to digital converter (sections 2, 3, 4, 10, 11).

In addition the functionning of the TDA8766G is shortly described (sections 1, 5, 7, 8) and several methods to provide input offset and top and bottom references are shown (sections 5, 6).

## CONTENTS

| 1. INTRODUCTION                                                                                                                   | 6         |

|-----------------------------------------------------------------------------------------------------------------------------------|-----------|

|                                                                                                                                   |           |

| 2. CONNECTOR, SWITCH AND JUMPER POSITIONS                                                                                         | 7         |

| 3. CONNECTOR SWITCH AND JUMPER LIST                                                                                               | 8         |

| <u>4. INITIAL SETTINGS : 3.3 V ADC SUPPLIES, AC COUPLED INPUT, 20 MHZ CLOCK</u><br>(ON BOARD), 3.3 V AND 1.2 V VOLTAGE REFERENCES | <u> </u>  |

| 5. VOLTAGE REFERENCES                                                                                                             | 13        |

|                                                                                                                                   |           |

| 5.1 TOP AND BOTTOM REFERENCES DERIVED FROM A POWER SUPPLY<br>5.2 TOP AND BOTTOM REFERENCES DERIVED FROM REFERENCE VOLTAGE         | 15        |

| <b>REGULATOR(S)</b>                                                                                                               | 16        |

| 6. INPUT OFFSET                                                                                                                   | <u>19</u> |

| 6.1 INPUT OFFSET DERIVED FROM A RESISTOR BRIDGE                                                                                   | 19        |

| 6.2 INPUT OFFSET DERIVED FROM THE MEDIUM REFERENCE                                                                                | 20        |

| 6.3 INPUT OFFSET PROVIDED BY AN OPERATIONAL AMPLIFIER                                                                             | 22        |

| 7. CLOCK                                                                                                                          | 24        |

| 7.1 CLOCK INPUT                                                                                                                   | 24        |

| 7.2 CLOCK JITTER                                                                                                                  | 27        |

|                                                                                                                                   |           |

**11.3 COMPONENT PLACE**

33

| 8. ADC SUPPLIES                                                             | 28                       |

|-----------------------------------------------------------------------------|--------------------------|

| 9. 10 BIT D/A CONVERTER                                                     | 28                       |

| 10. HOW TO CHANGE THE ADC SUPPLIES                                          | 29                       |

| <b>11. DEMO BOARD DOCUMENTATION : ELECTRICAL DIAGR</b><br>& COMPONENT PLACE | AM, COMPONENT LIST<br>29 |

| 11.1 ELECTRICAL DIAGRAM<br>11.2 COMPONENT LIST                              | 29<br>31                 |

## 1. INTRODUCTION

The TDA8766G is a 10 bit high speed, low voltage, low power analog to digital converter (53 mW typical at 3.3 V, 4 mW in standby mode).

It has been designed for video signal digitizing, radio communication, camcorders & all applications where size and power saving are strong requirements.

The supplies can be set in the range of 2.7 V up to 5.25 V (down to 2.5 V for output supply). The sampling frequency can reach 20 MHz.

Digitizing of 10 Mhz full scale square wave signal (shape of CCD output signal) with the 10 bit resolution is allowed if the settling time (max. 6 ns) and the signal slope (max. 0.4 V/ns) are respected.

Application requires few external components.

TDA8766G comes in a plastic thin quad flat package LQFP32 (SOT401-1), with the following overall body dimensions:  $5 \times 5 \times 1.4 \text{ mm}^3$ .

The present demonstration board is intended to facilitate an evaluation of the main TDA8766 characteristics. It is realized with a three layer PCB (one internal ground plane).

The following features are included :

- 20 MHz on-board quartz oscillator or a connection for an external clock.

- ADC voltage supplies, analog input offset, top and bottom voltage references are adjustable by the means of potentiometers (PCB supply is 8 V).

- Connectors allow external voltage references & external output supply (VDDO).

- DC or AC input signals are allowed. The input offset can be provided in three different ways :

by a resistor bridge by a resistor connected to the middle reference voltage (pin 11) by an external voltage source

- A 10 bit D/A converter has been added on the board to verify the good operation of the ADC with an oscilloscope. Because this D/A converter is not perfect, its analog output should not be used to characterize the TDA8766G.

6

**WARNING**: the on board D/A converter does not withstand a low output load; so it is necessary to check the strobe/scope input impedance before connection.

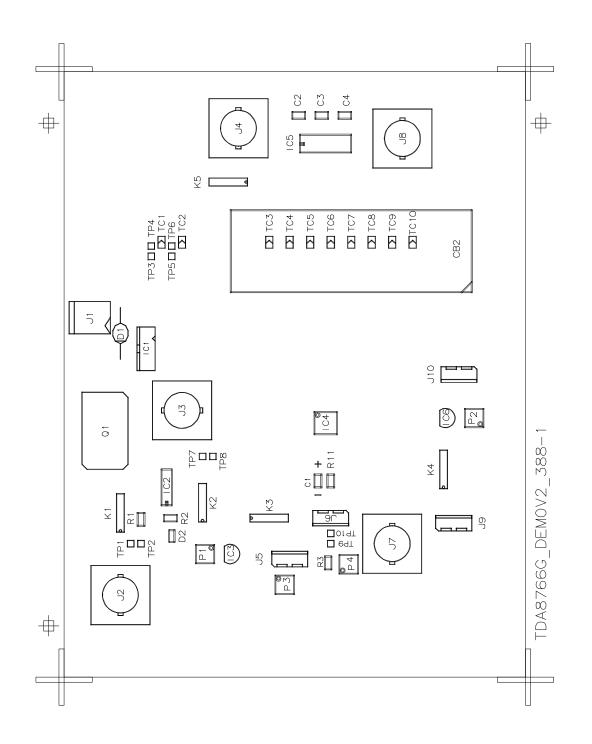

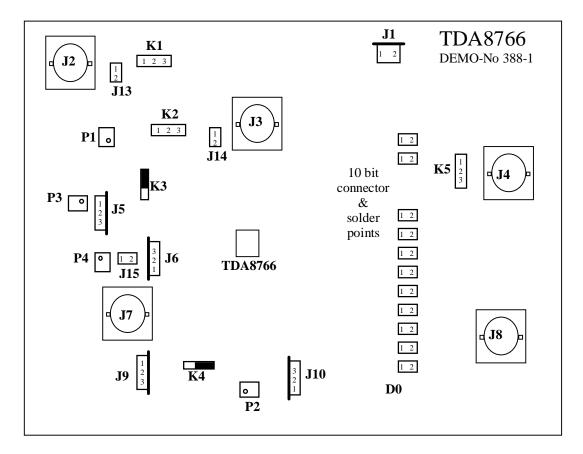

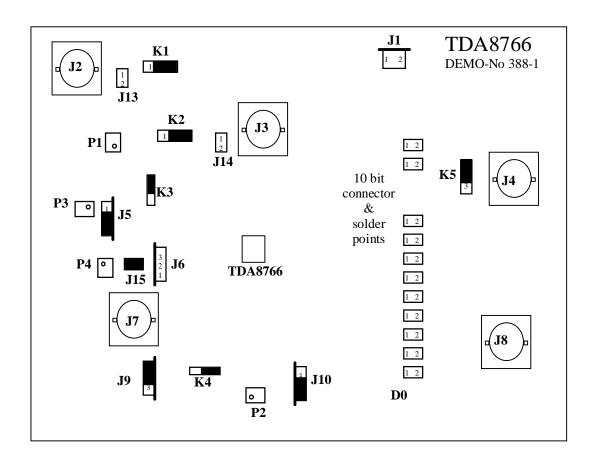

## 2. CONNECTOR, SWITCH AND JUMPER POSITIONS

## 3. CONNECTOR SWITCH AND JUMPER LIST

| Reference | Туре                        | Function                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J1        | 2 point connector           | External board supply (8V)                                                                                                                                                                                                                                                                                                                                                               |

| J2        | BNC                         | ADC (or ADC+DAC) clock input (50 $\Omega$ input)                                                                                                                                                                                                                                                                                                                                         |

| J3        | BNC                         | In range output (digital output)                                                                                                                                                                                                                                                                                                                                                         |

| J4        | BNC                         | DAC clock input (50 Ω input)                                                                                                                                                                                                                                                                                                                                                             |

| J5        | 3 point<br>connector/jumper | Internal/external bottom reference selection:<br>J5.1,Ground<br>J5.2,VBOT: Resistive load (1K potentiometer) must<br>be connected with J5.3 if internal bottom voltage<br>reference is used.<br>J5.3,VBOT-ext: Pin for external bottom voltage<br>reference connection.                                                                                                                  |

| J6        | 3 point<br>connector/jumper | Internal offset (provided by VMED)/external input<br>offset selection<br>J6.1, IN-DC: This pin allows DC input connection or<br>external input offset.<br>J6.2, VMED: Vmedium voltage reference. Vmedium<br>can be use to provide input offset (If it is well<br>decoupled from the input signal by the R11, C1<br>cell). In that case J6.1 and J6.2 must be connected.<br>J6.3, Ground. |

| J7        | BNC                         | Signal input (50 Ω input)                                                                                                                                                                                                                                                                                                                                                                |

| J8        | BNC                         | DAC output (high impedance probe is necessary)                                                                                                                                                                                                                                                                                                                                           |

| J9        | 3 point<br>connector/jumper | Internal/external top reference selection:<br>J9.1, VTOP-ext: Pin for external top voltage<br>reference connection, must be connected with J9.2<br>if internal top voltage reference is used.<br>J9.2, Internal top voltage reference<br>J9.3, Ground                                                                                                                                    |

| Reference | Туре                        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J10       | 3 point<br>connector/jumper | Internal/external VDDO supply selection<br>J10.1,VDDO: Digital supply (VDDD),<br>J10.2,VDDO-ext: External input for VDDO.<br>TDA8766 accepts from 2.5V to 5.25V as the VDDO<br>supply range. Must be connected with J10.1 if the<br>internal VDDO is selected. If the internal VDDO is<br>chosen, then VDDO=VDDD=VCCA.<br>J10.3, Ground.                                                                                                                                                                                                                                                                                           |

| J13       | 2 point jumper              | External clock direct connection<br>Must be connected if external ADC clock is<br>selected (In this case 5V to 3V logic level shifter is<br>bypassed).                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| J14       | 2 point jumper              | Clock test point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| J15       | 2 point jumper              | Internal input signal offset (provided by a resistor<br>bridge) connection<br>A resistor bridge (P4,R3,R7,C14) can be used to<br>provide the input offset. In that case J15.1 and<br>J15.2 must be connected. This resistor bridge is<br>supplied by the top voltage reference.                                                                                                                                                                                                                                                                                                                                                    |

| K1 &K2    | 3 point jumpers             | <ul> <li><u>External/internal clock selection and 5V to 3V logic level shifter cell connection.</u></li> <li>K1.1 &amp; K1.2 connection: J2 ADC CLK input is connected to the 5 to 3V level shifter cell and to the K5 jumper.</li> <li>K1.2 &amp; K1.3 connection: Internal clock oscillator is connected to the 5 to 3V level shifter cell and to the K5 jumper.</li> <li>K2.1 &amp; K2.2 connection: Direct connection between the external clock and the TDA8766 clock input is allowed.</li> <li>K2.2 &amp; K1.3 connection: The 5 to 3 V logic level shifter cell output is connected to the TDA8766 clock input.</li> </ul> |

| Reference | Туре           | Function                                                                                                                                                                     |

|-----------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| K3        | switch         | Stand-by control<br>Upper position STB=0 (standby off)                                                                                                                       |

|           |                | Lower position STB=1 (standby on)                                                                                                                                            |

| К4        | switch         | Output enable<br>Left position OE=1 (output high impedance)<br>Right position OE=0 (chip enabled)                                                                            |

| К5        | 3 point jumper | Internal/external clock selection for the DAC<br>K5.1 & K5.2 connection: Internal or ADC clock<br>selection<br>K5.2 & K5.3 connection: External DAC clock (J4)<br>selection. |

## 4. INITIAL SETTINGS : 3.3 V ADC SUPPLIES, AC COUPLED INPUT, 20 MHz CLOCK (ON BOARD), 3.3 V and 1.2 V VOLTAGE REFERENCES

The board supply must be set at 8 V.

In this configuration the analog input signal source must be provided by an external generator which is connected to the board by the J7 connector (dynamic input impedance: 50  $\Omega$ ).

The ADC supplies are provided by an adjustable precision regulator (TL431, IC6). The ADC supplies are adjustable from 2.7 V (2.5 V for VDDO) up to 5.25 V by the means of the P2 potentiometer.

The analog signal input offset is derived from the ADC analog supply through a resistor bridge (R7,R3,C14, and potentiometer P4). It is adjustable thanks to P4. Top & bottom voltage references are provided simply and economically :

The top reference voltage is provided by an adjustable precision regulator (TL431, IC3).

The bottom reference is provided by a simple resistor load (potentiometer P3). The top and bottom reference can be adjusted by the means of P1 and P3 potentiometers respectively.

To obtain this operational mode, jumpers and switches are set as shown in the following figure.

Potentiometers P1, P2, P3, P4 are adjusted as explained in the following.

P1 is used for the top reference voltage adjustement. To obtain 3.3V, P1 is set around 157  $\Omega.$

P2 potentiometer is used to adjust the ADC and the 74LVC86D supplies. In order to obtain 3.3 V supplies, P2 is adjusted around 157  $\Omega$ . (See section 8 for more information about supplies)

P3 allows the adjustment of the bottom voltage reference. In order to obtain a bottom reference of 1.2 V, P3 is adjusted around 165  $\Omega$ . See section 5 for more information about references.

P4 allows the adjustment of the input offset. In order to obtain an input offset of 2.25 V, P4 is adjusted around 2093  $\Omega$ . (See section 6 for more information about input offset)

## 5. VOLTAGE REFERENCES

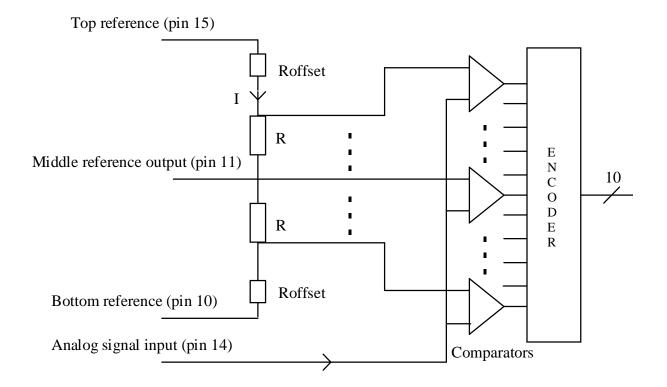

Here is a block diagram which explains the TDA8766 working:

During the A to D conversion the analog input signal (pin14) is compared to voltage references by the means of voltage comparators (In fact these comparators are folding amplifiers).

The full scale analog signal input range (FS) is given by: FS=0.871 (Top ref. - Bottom ref.) ; The 0.871 coefficient is due to the two offset resistors.

The comparator voltage references are derived from a resistor ladder which is supplied through Vtop (pin 15) and Vbottom (pin 10). Therefore if the Vtop and Vbottom are not well regulated the A to D conversion will be affected.

| TDA8766G                       |

|--------------------------------|

| Evaluation board documentation |

Top reference (pin 15) is the highest voltage reference and the bottom reference (pin 10) is the lowest voltage reference. Consequently a current I is flowing from pin 15 to pin 10.

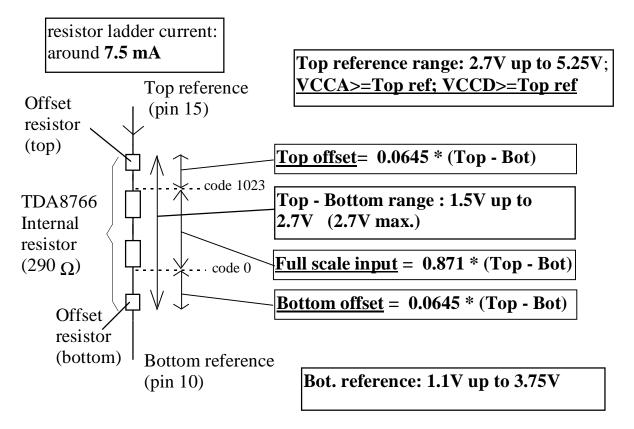

The typical value for the internal resistor ladder is 290  $\Omega$  at 25°C.

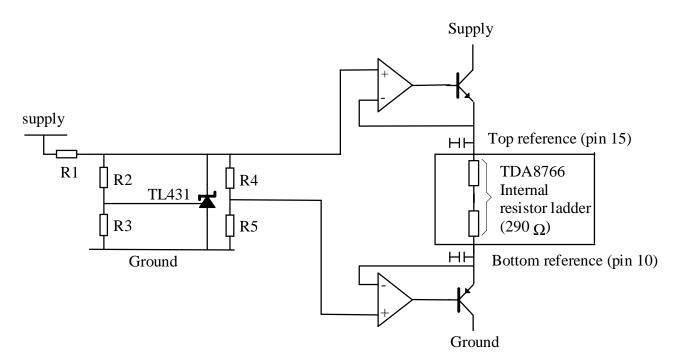

As shown in the following schematic the TDA8766 is versatile in the choice of the top voltage reference, bottom voltage reference and power supplies. So it will be easy to find top and bottom voltage references which fit with the majority of the applications.

Regulation of Vtop & Vbottom depends on the level of cost and quality that are required by the customer application.

| TDA8766G                       |  |

|--------------------------------|--|

| Evaluation board documentation |  |

Several methods providing these voltage references are shown in this section.

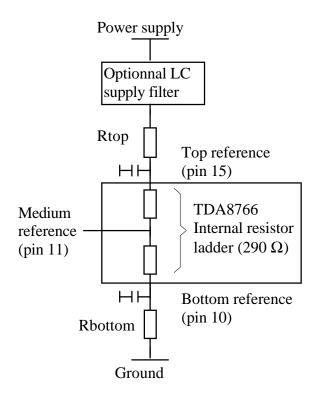

## 5.1 TOP AND BOTTOM REFERENCES DERIVED FROM A POWER SUPPLY

If the power supply is well regulated a simple resistor string stucture will be efficient (see following figure).

It is possible that the top reference equal the power supply voltage. So the Rtop resistor can be removed. An optional filter can be added on the analog supply (depending on supply noise level).

Typical voltages for a 3.3V application are 3.3V for the top reference and 1.2V for the bottom reference The current flowing through the 290  $\Omega$ resistor ladder is 7.24 mA. So Rtop=0 and Rbottom=160 $\Omega$ .

Remarks: here, the spreads due to process and temperature are not taken into account.

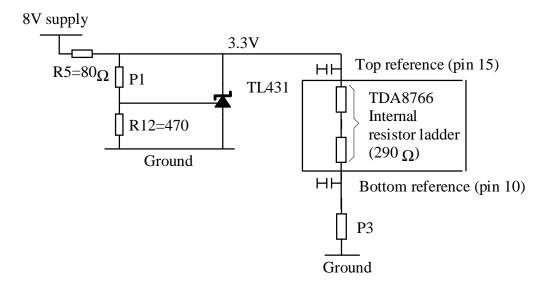

# 5.2 TOP AND BOTTOM REFERENCES DERIVED FROM REFERENCE VOLTAGE REGULATOR(S)

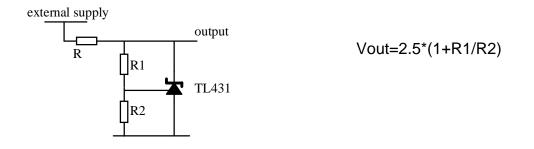

In some cases (noise on supply, several ADC's mounted in parallel ...) solutions with precision regulators (Philips uA723, Texas TL431,...) may be preferred. On this board a regulator for the top voltage reference is provided (IC3,TL431), whereas the bottom reference is simply provided by a potentiometer (P3):

TL431 output=2.5 \*(1+P1/R12) V

Two connectors on the board, J9 (for top reference) and J5 (for bottom reference), allow connection of external references.

If several ADC are mounted in parallel, or if a very high precision of the voltage references over the whole temperature range is required, the following schematic can be used :

Operational amplifier with a low input offset should be used. The transistor types depend on the number of TDA8766G mounted in parallel. (7.5 mA typ. for one TDA8766G)

If only one ADC is used the operational amplifier and the transistor which drives the top reference can be skipped. In this case, the voltage regulator directly drives the top reference.

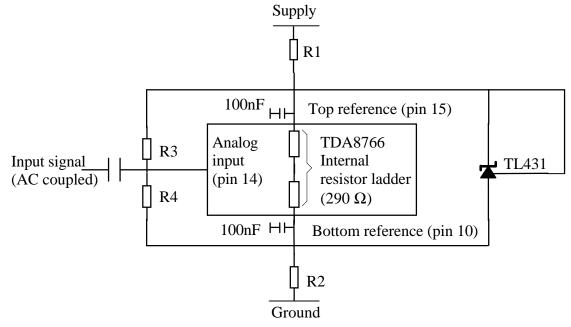

In the following electrical diagram, top and bottom references are regulated by only one component (TL431):

The (top - bottom) difference is set at 2.5V by the TL431, so the full scale input is set at 0.871\*2.5=2.18V. In addition the input offset is set at (Vtop+Vbottom)/2 by two equal resistors (R3 and R4).

In this case the TL431 maintains the (top - bottom) difference at 2.5V over temperature and supply variations. Because the input offset is derived from the top and bottom references, it is also regulated at (Vtop+Vbottom)/2 over the temperatureand supply variations.

Using this method it is possible to drive the input offset and the top and bottom references of several TDA8766G with a very good matching with only one TL431. Typical resistor values for a 5V application and for one TDA8766G are:

$R3=R4=2.2K\Omega$ , R1=R2=82 $\Omega$ . The current flowing trough the R1, R2 resistors is around 15mA (The TL431 requires a minimum current to provide a good regulation).

## 6. INPUT OFFSET

When AC coupling is used with the TDA8766 it is necessary to provide an input offset in order to respect the TDA8766 full scale input range.

Relations between the Vtop reference, the Vbottom reference, the maximum amplitude of the analog signal and the input offset are:

Maximum amplitude of analog signal is (Vtop-Vbot)\* 0.871 and the input signal is centered around the input offset which is (Vtop+Vbottom)/2.

Consequently, if Vtop = 3.3 V and if Vbottom = 1.2 V the maximum amplitude of the analog signal is 1.83 V and the input offset is 2.25V; code 0 is obtained for a 1.335V input, and code 1023 is obtained for a 3.165 V input.

Input offset can be provided by many different methods; several methods are explained in this section.

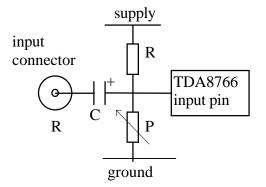

## 6.1 INPUT OFFSET DERIVED FROM A RESISTOR BRIDGE

When a resistor bridge is used to provide an offset the current flowing through the resistors must be at least 10 times greater than the signal current (TDA8766 analog input current is 0 to 35  $\mu$ A) in order to guarantee the stability of the input offset. Consequently the resistive value of this resistor string must be below 8.5 k $\Omega$  (with a 3 V supply).

If the input signal generator used to test the TDA8766 requires a 50  $\Omega$  load, R must be set at 73.33  $\Omega$  and P at 157.14  $\Omega$  (Vtop=supplies=3.3 V,Vbottom=1.2 V), in order that the dynamic impedance (R & P in parallel) be 50  $\Omega$ .

## Remarks:

- This method provides a correct input offset but the current flowing through the resistor bridge is high: 14mA (R=75 $\Omega$ , P=157 $\Omega$  and 3.3V supply).

In order to reduce this current consumption another method is used on board but it requires two more components (one capacitor and one resistor) :

R3 is equal to the output load of the external signal generator. C14 allows ground connection between R3 and P3 in dynamic mode. Typical values when a 50  $\Omega$  signal generator is used are: R7=1K  $\Omega$ , R3=50  $\Omega$ , P3=5 k $\Omega$  (set at 2093  $\Omega$ ), C14=10 nF, then the current flowing through the resistor bridge is only 1.05 mA with a 3.3 V top reference. The solder print of an optional resistor R8 is provided in order to

resistor R8 is provided in order to allow other impedance adaptations.

- When it is possible, it is better to replace the potentiometers by fixed resistors. This will avoid possible distortion effects on the input signal due to the capacitive components of the potentiometers.

- It can be difficult to obtain the exact output load and the exact input offset when they are made up of fixed resistors, because the accuracy of the resistors is limited. Consequently in some professional applications it is better to provide the correct load and the correct input offset by means of operational amplifiers.

## 6.2 INPUT OFFSET DERIVED FROM THE MEDIUM REFERENCE

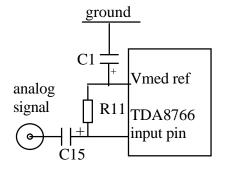

In this case the input pin is connected to the medium voltage reference (pin 7) by the means of a resistor (R11). The medium voltage reference must be well decoupled by a capacitor (C1). The input impedance of the AD converter is given by R11 in parallel with Zin.

| TDA8766G                       |  |

|--------------------------------|--|

| Evaluation board documentation |  |

This method gives good results in the following domains : high common mode supply rejection (because both the voltage references and the input offset are derived from the same supply), very low noise level and low cost. R11\*C1 product must be high enough in order to avoid a coupling between the input signal and the medium reference. (C1=4.7 $\mu$ F for example) The offset on the input pin is: Vmed - (17 $\mu$ A\*R11)

On board selection of the input offset, provided by the medium reference, is allowed by the J6.1 & J6.2 connection. In this case R11 and C1 must be soldered (SMD 1206 series solder prints).

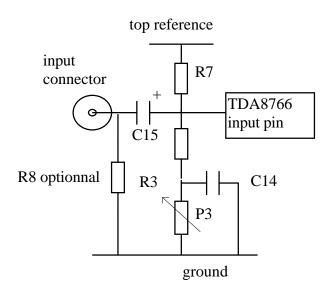

## 6.3 INPUT OFFSET PROVIDED BY AN OPERATIONAL AMPLIFIER

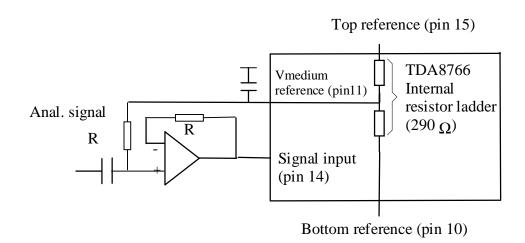

The middle output reference voltage and a low input offset operational amplifier can be used to provide an accurate input offset. Several methods can be used :

1°)

The R resistor in the op-amp loop compensates the offset due to the R resistor connected to Vmed. (R=1k $\Omega$ ; C=1 $\mu$ F)

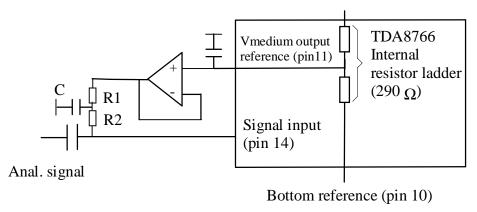

2°)

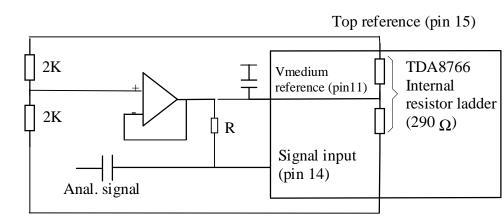

Top reference (pin 15)

3°)

| TDA8766G                       | Application Note |

|--------------------------------|------------------|

| Evaluation board documentation | AN96012          |

The amplifier does not need a high bandwidth, but the necessary time to load the C capacitor at 'power on' depends on the op.amp maximum output current. The input impedance is R2 // Zin. Zin is the ADC input impedance.

Bottom reference (pin 10)

Medium reference is derived from top and bottom reference (input impedance is R  $\prime\prime$  Zin).

## 7. CLOCK

## 7.1 CLOCK INPUT

On the demo-board several methods can be used (depending on switch positions) to provide the ADC clock (see sections 2,3). Precautions must be taken if the high clock level is higher than the VDDD level.

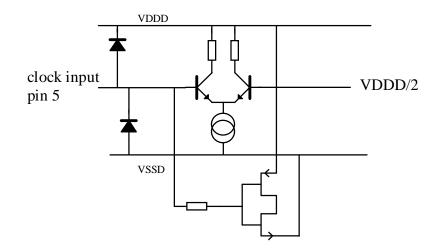

In fact, the TDA8766 clock input (pin 5) is protected by diodes (see figure):

If the high clock level is greater than VDDD+0.5 V, a current will flow between the clock input & VDDD through the protection diode. This will affect the proper functioning of the ADC.

Consequently, it is necessary to keep the high clock level below VDDD+0.5 V. Several methods can be used to limit high clock level :

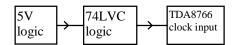

1- Use of a 3 V logic device as a 5 to 3 V interface (Philips LVC logic family for example).

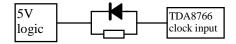

2- Use of a parallel resistor/diode network in series with 5 V output.

The resistor limits current and voltage supplied to the TDA8766. The diode allows a faster high to low transition (R=470 $\Omega$ , D=BAS16/BAS32...).

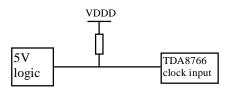

3- In case of 5 V logic with an open drain output, use a pull-up resistor connected to the low voltage supply.

For each method It is possible to test the influences on ADC performance of each method with the demo-board. A 74LVC86D is used as a 5V logic to 3V logic level translator. SMD resistors and diodes solder prints are provided to allow the testing of the diode/resistor network (R2, D2) and the testing of the pull-up resistor (R1).

#### ON BOARD / EXTERNAL CLOCKS SELECTION (SUMMARY):

IC2 (low voltage logic xor gates), K1, K2, K5, J13 (jumpers), R1, R2, R4, R6 (resistors), D2 (diode), allow a wide choice of ADC & DAC clock sources. The following settings are possible :

- A 20 MHz TTL on-board quartz oscillator can be chosen with K1 & K5.

- Direct external clock connection is also possible by means of the J2 & J13.

- On board or external clock can be used independently for both ADC & DAC.

- The clock can be connected directly to the ADC or through a 5V to 3V logic interface (R2, R1, D2, IC2). Therefore, logic with open collector output, standard CMOS logic, or standard TTL logic, can be connected to the board.

## 7.2 CLOCK JITTER

If the clock jitter and the slope of the analog input signal are high, sampling errors can appear.

Example :

The equation of a sinewave signal is  $s(t)=A/2 \sin(2 \pi F t)$ , where A is the ADC full scale amplitude (A=1024 LSB) and F is the sinewave frequency.

The slope of this signal is given by:  $ds(t)/dt=A/2 2 \pi F cos(2 \pi F t)$

This slope is maximum when t=0 (input voltage level is around middle code 511/512):

ds(0)/dt=A  $\pi$  F Volt/second.

That means that the middle code is available at the ADC input only during:

**Tisb=LSB/(A**  $\pi$  **F)=(1024**  $\pi$  **F**)<sup>-1</sup> second.

If the full scale sinewave frequency is F = 10 MHz, then Tlsb = 31 psConsequently the clock jitter must be lower than this value.

If a 20 Mhz full scale sinewave is sampling the jitter must be lower than 15 ps.

## **Remarks:**

If the sample clock frequency and the input signal frequency have the same jitter (or phase noise), the sampling error due to jitter can be avoided. Therefore it is not suitable to do precise dynamic measurements of the ADC characteristics with the on board quartz oscillator. (Except if the input signal frequency and the quartz oscillator frequency are correlated).

Application Note AN96012

## 8. ADC SUPPLIES

ADC and 74LVC86D supplies are provided by an adjustable voltage regulator (TL431,IC6).

The DAC supplies are set to 5 V (by the means of a 7805 regulator). The IC6 regulator output voltages are adjustable by a resistor ratio (see figure). The formula which gives the regulated voltage related to the resistor ratio is :

The power consumption of each TL431 is volontarily set higher than necessary in order to allow different ADC voltage supplies. See section 10: how to change the ADC supplies.

## 9. 10 BIT D/A CONVERTER

A 10 bit 5 V supply/TTL input DAC (IC5) allows **rough** ADC evaluation with a scope or a spectrum analyzer. Analog output level is in the range of 3 to 5 V.

**WARNING**: This D/A converter does not support low output loads, so it is necessary to check the strobe/scope input impedance before connection to the load.

## 10. HOW TO CHANGE THE ADC SUPPLIES

The TDA8766G can work with all supply voltages in the range of 2.7 V to 5.25 V: analog supply (VDDA), digital supply (VDDD), output supply (VDDO). Furthermore, VDDO can be set as low as 2.5 V.

The only restriction for the supplies is to respect the following conditions:

-0.2V < VDDA-VDDD < 0.2V -0.2V < VDDD-VDDO < 3V -0.2V < VDDA-VDDO < 3V

Adjustment of the ADC supplies in the range of 2.7 V to 5 V is achieved by the adjustment of P4 potentiometers (see section 8).

Separate adjustment of VDDO is possible if an external supply is connected to J10. Be sure to respect the limit differences between the supplies.

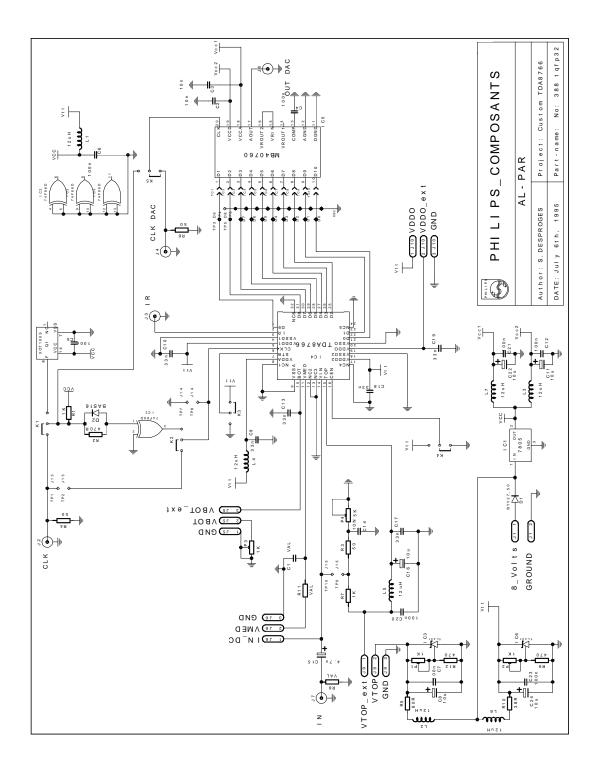

## 11. DEMO BOARD DOCUMENTATION : ELECTRICAL DIAGRAM, COMPONENT LIST & COMPONENT PLACE

## 11.1 ELECTRICAL DIAGRAM

(see next page)

## **11.2 COMPONENT LIST**

| Reference                                                                                                                                                                                                                | Value                                                                                                                 | Component                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C1<br>C2<br>C3<br>C4<br>C5<br>C6<br>C7<br>C8<br>C9<br>C10<br>C11<br>C12<br>C13<br>C14<br>C15<br>C16<br>C17<br>C18<br>C19<br>C20<br>C21<br>C22<br>C23<br>C24<br>CB2<br>D1<br>D2<br>IC1<br>IC2<br>IC3<br>IC4<br>IC5<br>IC6 | 33 μF<br>33 nF<br>10 μF<br>100 nF<br>33 nF<br>10 nF<br>4.7 μF<br>10 μF<br>33 nF<br>33 nF<br>33 nF<br>100 nF<br>100 nF | C1206<br>C1206<br>C1206<br>C1206<br>SPRAGUE_595D_A<br>C805<br>C805<br>SPRAGUE_595D_A<br>C1206<br>C805<br>C805<br>SPRAGUE_595D_A<br>SPRAGUE_595D_A<br>C805<br>C805<br>C805<br>C805<br>C805<br>C805<br>C805<br>C805 |

| Reference | Value     | Component      |

|-----------|-----------|----------------|

| J1        |           | CONN353MV2     |

| J2        |           | BNC            |

| J3        |           | BNC            |

| J4        |           | BNC            |

| J5        |           | CONN1X3V_FCON  |

| J6        |           | CONN1X3V_FCON  |

| J7        |           | BNC            |

| J8        |           | BNC            |

| J9        |           | CONN1X3V_FCON  |

| J10       |           | CONN1X3V_FCON  |

| K1        |           | 3 POINT JUMPER |

| K2        |           | 3 POINT JUMPER |

| K3        |           | SWITCH         |

| K4        |           | SWITCH         |

| K5        |           | 3 POINT JUMPER |

| L1        | 12µH      | LQH4N          |

| L2        | 12µH      | LQH4N          |

| L3        | 12µH      | LQH4N          |

| L4        |           | LQH4N          |

| L5        | •         | LQH4N          |

| L6        |           | LQH4N          |

| L7        |           | LQH4N          |

| P1        | 1K        | 3224W          |

| P2        | 1K        | 3224W          |

| P3        | 1K        | 3224W          |

| P4        | 5K        | 3224W          |

| Q1        |           | X071009        |

| R1<br>R2  | 1K<br>470 | RMR01          |

|           |           | RMR01          |

| R3<br>R4  |           | RMR01<br>RMR01 |

| R4<br>R5  |           | RMR01          |

| R6        |           | RMR01          |

| R7        |           | RMR01          |

| R8        | 50        | RMR01          |

| 1.0       | 50        |                |

| Reference | Value | Component                          |

|-----------|-------|------------------------------------|

|           |       |                                    |

| R9        | 470   | RMR01                              |

| R10       | 38    | RMR01                              |

| R11       | 1K    | RMR01                              |

| R12       | 470   | RMR01                              |

| TC1-TC10  |       | SOLDER POINTS                      |

| TP1-TP2   | J13   | TEST POINTS (jumper)               |

| TP3-TP6   |       | TEST POINTS 2 BIT CONNECTOR (MSBs) |

| TP7-TP8   | J14   | TEST POINTS (clock)                |

| TP9-TP10  | J15   | TEST POINTS (jumper)               |

|           |       |                                    |

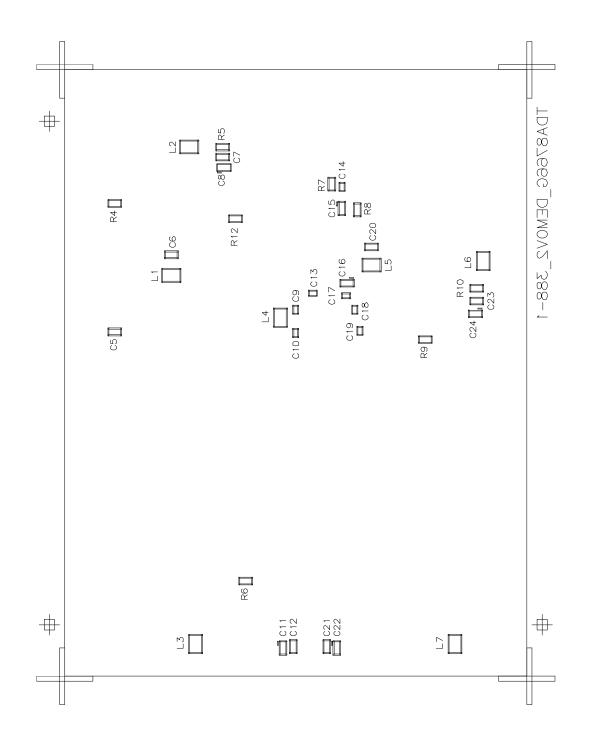

## **11.3 COMPONENT PLACE**

(see next page)